[This post was edited to show the results with version 1.1 of the test]

Some updates, I actually found another issue: I modified my program to use the VIA timer 2 to accurately measure the time taken by some random routine when my sample player is running in the background (using an IRQ triggered by the VIA timer 1).

Based on that I ran five tests:

- Compute the time taken to just set the value of the timer2 and then read it immediately back to have a good base value

- Measure the time taken at startup on the Oric with just the normal 100hz system interrupt running (the one that reads the keyboad, blinks the cursor, handle internal timers, etc...)

- Measure the time when my sample player is not initialized, but with the interruptions disabled on the 6502 (instruction SEI before the test).

- Measure the time when my sample player is initialized (with the timer 1 setup), but with the interruptions disabled on the 6502 (instruction SEI before the test).

- Measure the time when everything is initialized and interruptions allowed on the 6502 (instruction CLI before the test).

I have to say that the results are entertaining

For the reference here is a screenshot taken on my TV connected to a real Oric Atmos 48k:

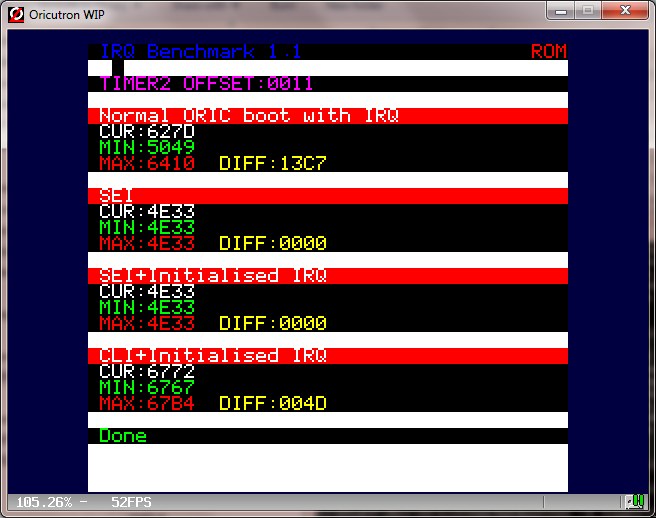

And here are the results we got from three different emulators:

-

Euphoric 1007:

-

Oricutron 0.7:

-

Mess 0143u2b:

As you can see the numbers are quite different, but from these we can give some conclusions:

- The base test returns $11 on the Atmos, both

Euphoric and

Oricutron are close with $12,

Mess is a bit faster with $f. So here we are between +1 and -2 cycles compared to the real machine.

- If you take into account this small difference in timer value reading, the

Mess seems to be remarkably similar to the real machine on the normal Oric setup: Same $13c3 difference, and $5047+2=$5049, $640a+2=$640c, so it's consistent with what my Atmos shows.

Euphoric has worse MAX value, but the diff is still relatively close.

Oricutron is the farther with $14C3 instead of $13C3, that's about 256 more clock cycles.

-

Euphoric is the only emulator which has different clock cycles values for the tests with SEI enabled, this means that for some strange reasons even with the 6502 not accepting any IRQ it still get somewhat some lost cpu time when you play with the VIA. Definitely a real bug here.

- When IRQ are disabled

Oricutron is almost like the reference Atmos, just off by plus one (465D instead of 465C), while

Mess is off by minus two (465A instead of 465C), that's consistent with the +1/-2 timer 2 reading difference we had at the start.

- The last test is the most interesting. Basically instead of the 100hz single interrupt (so that's two interrupts per frame) we have a 4khz interrupt (so that's 80 interrupts per frame).

Mess is actually still consistent there, showing the same values than the Atmos, minus two cycles.

Euphoric is about 662 clock cycles higher ($6a9c-6853) that the reference Atmos which divided by 80 would amount for about 8 additional clock cycle per IRQ.

Oricutron on the other hand is way to fast by 901 clock cycles ($6806-$6481), so that would be about 11 missing clock cycles per IRQ.

Stay tuned

PS: You can find the source code on the SVN server: http://miniserve.defence-force.org/svn/ ... Benchmark/

PS: You can find the source code on the SVN server: http://miniserve.defence-force.org/svn/ ... Benchmark/

The program itself is on the FTP: http://www.defence-force.org/ftp/forum/ ... Bench1.tap